This New ‘Skyscraper’ Chip Could Make Computers Run 1,000 Times Faster

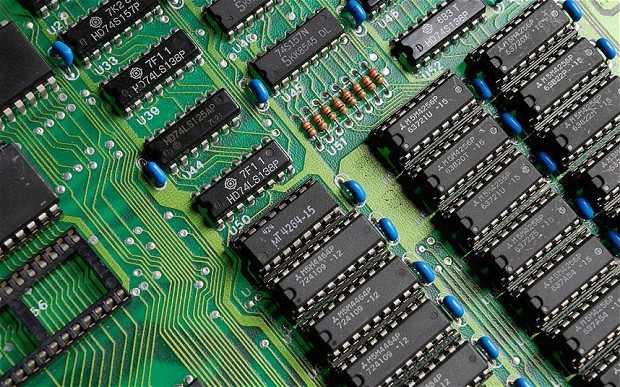

Short Bytes: Researchers and Engineers at Standford have fabricated a skyscraper chip which replaces the conventional Silicon chip and is much faster. Nanomaterials have been used in designing and fabrication of these chips.

Short Bytes: Researchers and Engineers at Standford have fabricated a skyscraper chip which replaces the conventional Silicon chip and is much faster. Nanomaterials have been used in designing and fabrication of these chips.

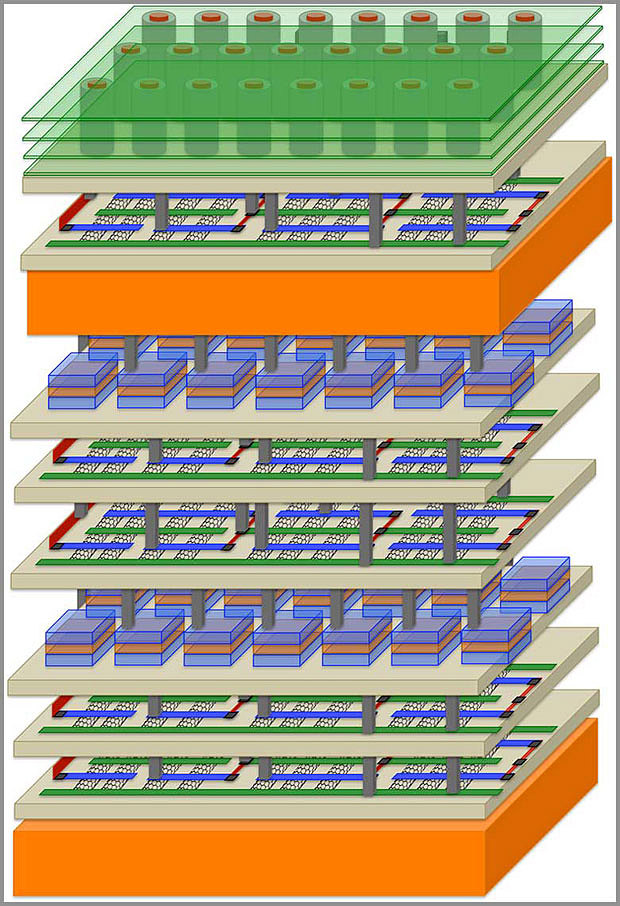

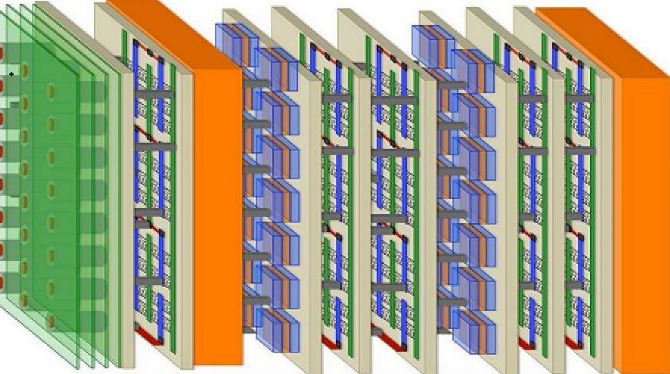

Referring to the conventional chip design method as suburb design where layouts create the traffic jam in the electronic circuit, thus wasting time and energy, Skyscraper chip will be much more efficient. The traffic jam bottleneck will be addressed by integrating processors and memories in the form of floors of a high rising building thus, creating an innumerable number of permutation and combination for the traffic flow and the energy consumption optimization.

In the past, such trials of creating stacked Silicon chips have been performed. However, due to extremely precise Silicon fabrication process, it needs extremely machine dexterity in stacking two Silicon chips together while fabrication. But, with Skyscraper approach, two Silicon chips can be fabricated differently and later, can be stacked over each other using thousand of wires, a relatively much easier approach. And keeping these points in view, new Skyscraper chip with Nano-material was fabricated. These nanomaterials are actually Carbon Nanotube transistors which have replaced conventional transistors in the design.

Surprisingly, the same team also has replaced conventional silicon chips with resistive random-access memory, or RRAM. RRAM uses tiny jolts of electricity to switch memory cells between the binary states of zero and one. Millions of devices called vias are used to connect each RRAM like tiny electronic ‘elevators’ that allow data to travel over much smaller distances than traditional circuits. The thermo-coolers installed in between the layers make sure that the generated heat does not accumulate, doing long term degradation.

To demonstrate the proof of concept, the same team also demonstrated a four-layer prototype model made from two layers of RRAM memory and two layers of CNTs at the 2014 International Electron Devices Meeting. In their upcoming IEEE paper, they have simulated the result showing how skyscraper approach is 1,000 times more efficient than conventional chip design system.

Are you hopeful about this revolutionary Skyscraper chip? Tell us in the comments below.

Source/Image credits: Stanford.edu

[adinserter block=”12″][adinserter block=”13″]